# Scaling Up Neuromorphic Systems for Breakthroughs in Computing

(intel)

Mike Davies | Director, Neuromorphic Computing Lab | Intel Labs November 18, 2019

## Legal Information

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Intel makes no representations or warranties regarding the accuracy or completeness of the information in this presentation. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel, the Intel logo, Movidius, Core, and Xeon are trademarks of Intel Corporation in the United States and other countries.

\*Other names and brands may be claimed as the property of others

Copyright © 2019 Intel Corporation.

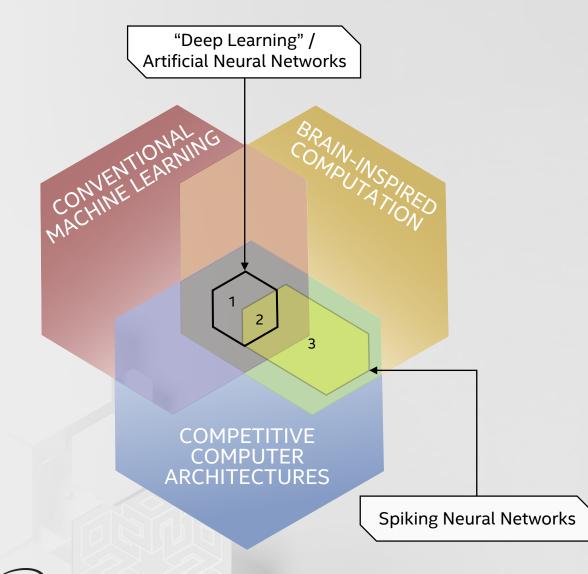

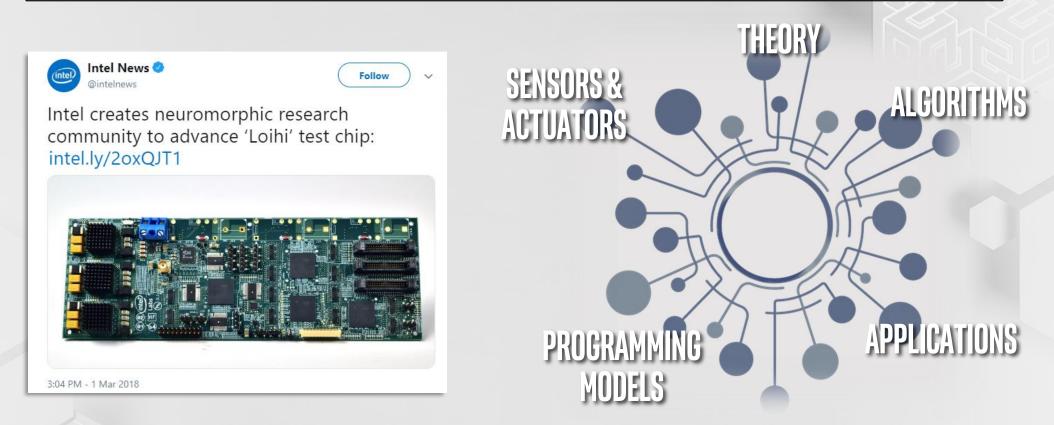

# **Neuromorphic Computing Exploration Space**

### **RESEARCH GOALS**

- Broad class of brain-inspired computation

- Efficient hardware implementations

- Scalable from small to large problems and systems

## EXAMPLE WORKLOADS

- Learning without cloud assistance

- Learning with sparse supervision

- Online and lifelong learning

- Probabilistic inference and learning

- Sparse coding

- Associative memory, similarity matching

- Nonlinear adaptive control (robotics)

- SLAM and path planning

- Constraint satisfaction

- Dynamical systems modeling

3

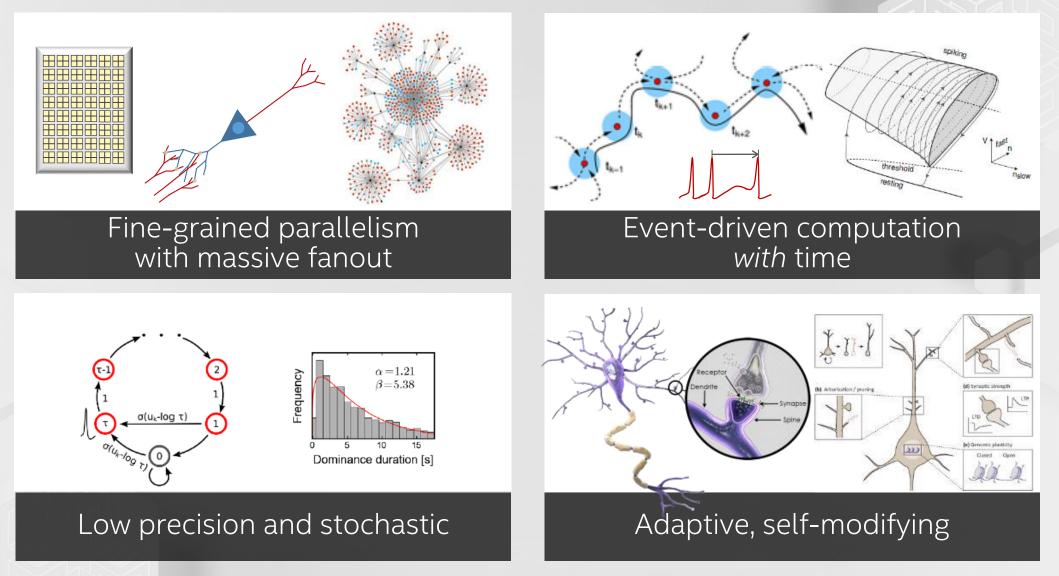

## Some Principles of Neural Computation

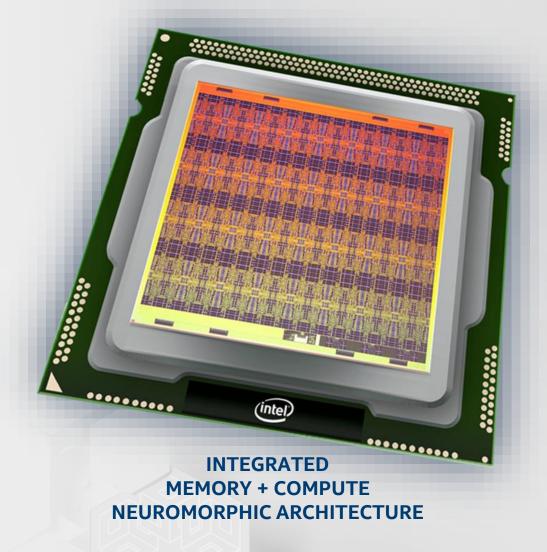

## Our Loihi Research Chip

#### **KEY PROPERTIES**

- 128 neuromorphic cores supporting up to 128k neurons and 128M synapses with an advanced spiking neural network feature set.

- Supports highly complex neural network topologies

- Scalable on-chip learning capabilities to support an unprecedented range of learning algorithms

- Fully digital asynchronous implementation

- Fabricated in Intel's 14nm FinFET process technology

Davies et al, "Loihi: A Neuromorphic Manycore Processor with On-Chip Learning." IEEE Micro, Jan/Feb 2018.

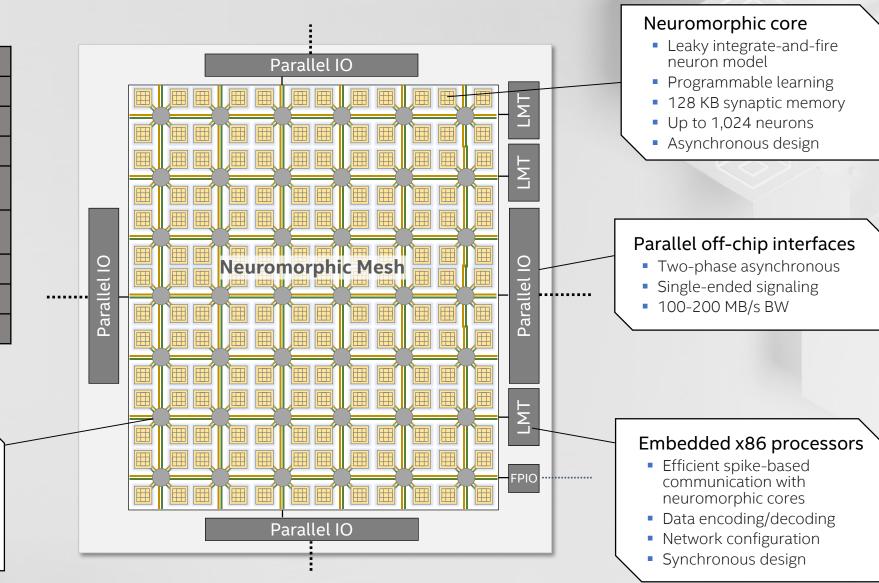

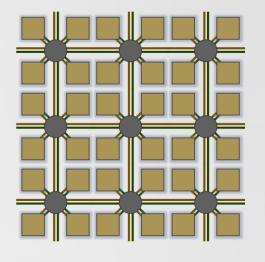

## **Chip Architecture**

| Technology:                                       | 14nm                         |   |

|---------------------------------------------------|------------------------------|---|

| Die Area:                                         | 60 mm2                       |   |

| Neuro cores:                                      | 128 cores                    |   |

| x86 cores:                                        | 3 LMT cores                  |   |

| Max #<br>neurons:                                 | 128K neurons                 |   |

| Max #<br>synapses:                                | 128M synapses                |   |

| Transistors:                                      | 2.07 billion                 |   |

| Memory:                                           | 33 MB                        | · |

| Efficiency:                                       | 42 GOPS/W                    |   |

|                                                   |                              |   |

| <ul><li>8x16-core 2</li><li>Scalable to</li></ul> | 1000's cores<br>order routed |   |

- Two physical fabrics

- 8 GB/s per hop

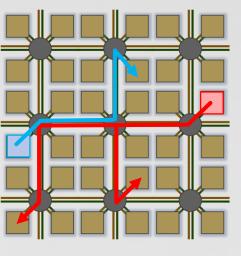

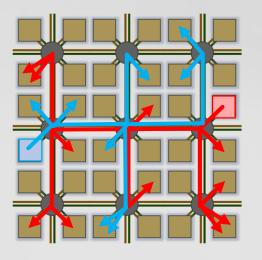

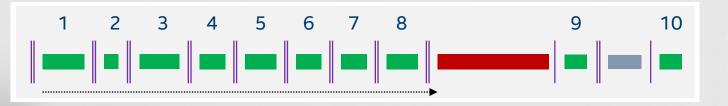

## Mesh Operation: Fine-Grained Synchronization

Time step T begins.

Cores update dynamic neuron state and evaluate firing thresholds

Above-threshold neurons send spike messages to fanout cores

(Two neuron firings shown.)

All neurons that fire in time T route their spike messages to all destination cores.

Barrier Synchronization messages exchanged between all cores.

When complete, time advances to time step T+1.

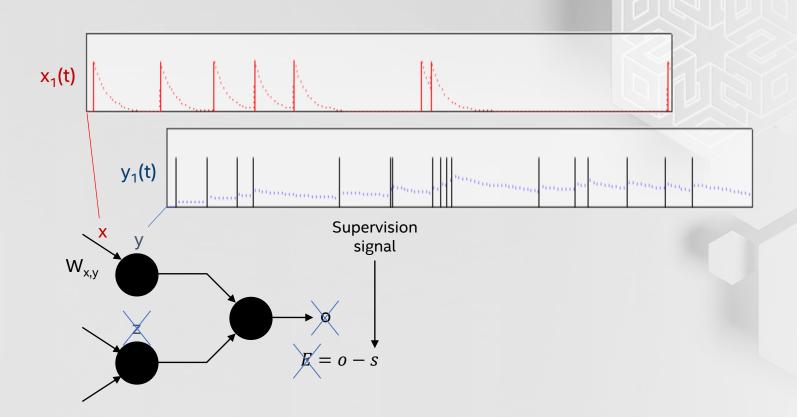

## Programmable Learning with Local Plasticity

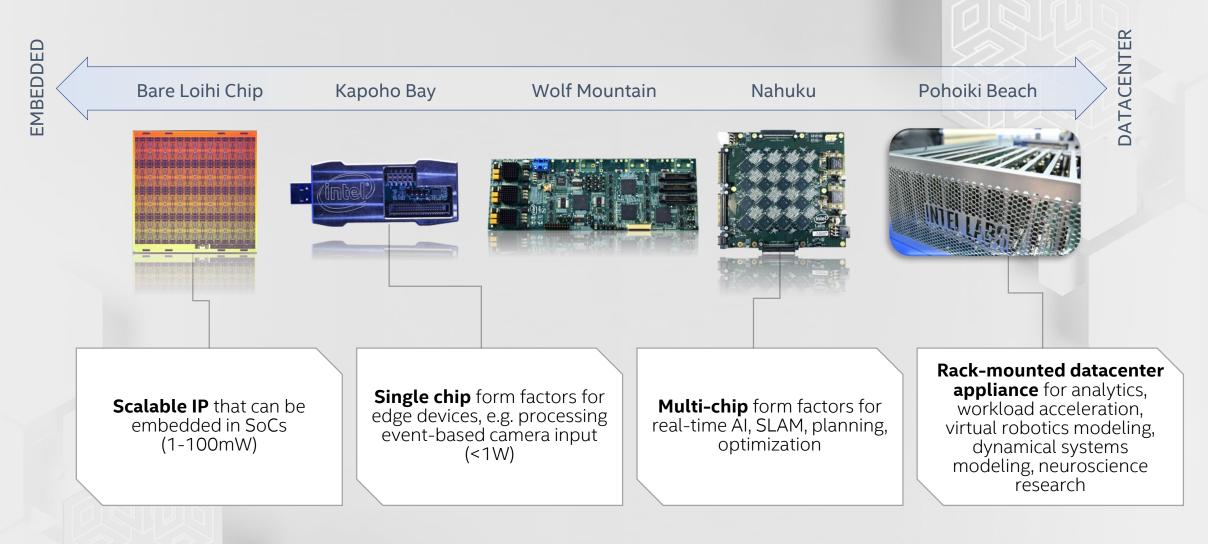

## Scalable from Embedded IP to Datacenter

(intel)

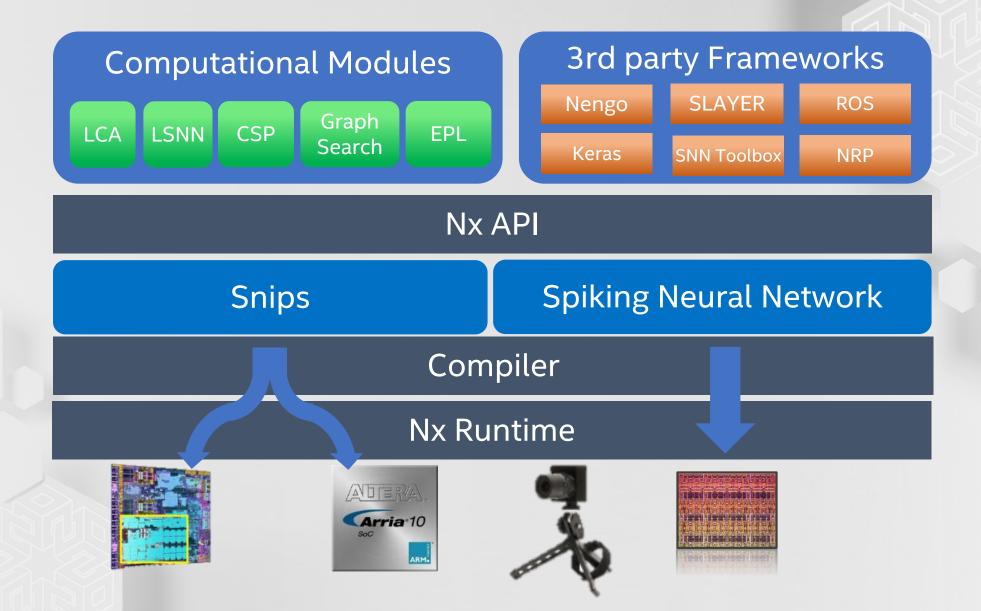

## Nx SDK Software Architecture

## Intel Neuromorphic Research Community

#### Collaborating to Accelerate the Research

75 ENGAGED ACADEMIC, GOVERNMENT, AND INDUSTRY GROUPS Email inrc\_interest@intel.com to get involved!

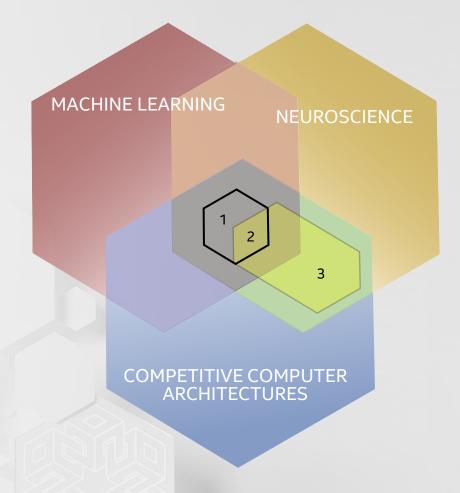

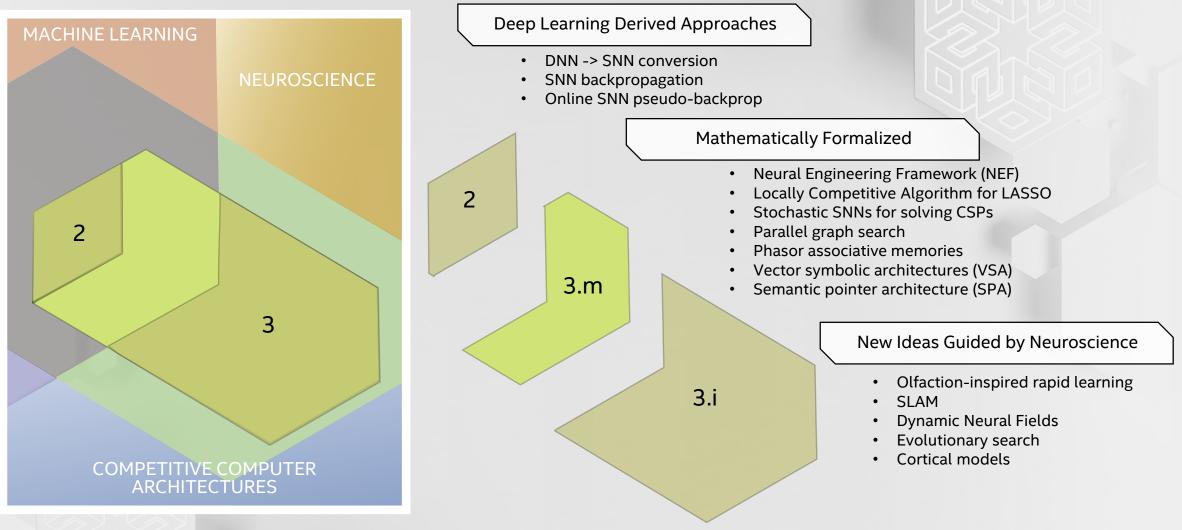

## The Challenge: SNN Algorithm Discovery

# The Challenge: SNN Algorithm Discovery

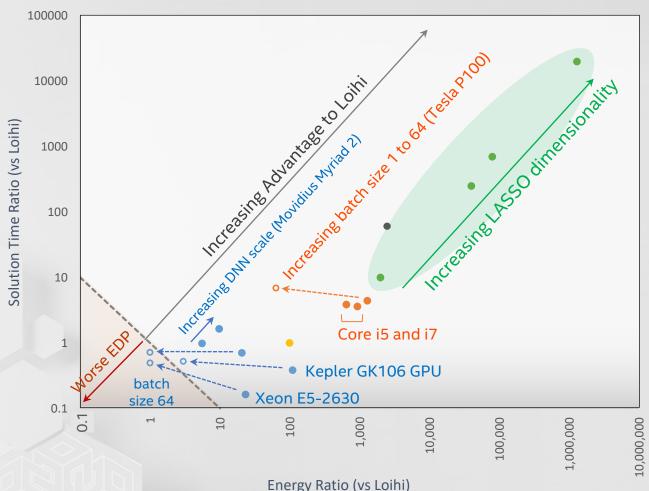

## Loihi Quantitative Results Summary

- Keyword Spotter DNN\*

- Keyword Spotter DNN\* (batch size >1)

- 1D SLAM\*\*

- Sequential MNIST (LSNN\*\*\*)

- Sequential MNIST (batch size 64)

- LASSO

GRAPH SEARCH

- ----- Unit energy delay product (EDP)

\* P Blouw et al, 2018. arXiv:1812.01739 \*\* G Tang et al, 2019. <u>arXiv:1903.02504</u> \*\*\* Bellec et al, 2018. arXiv:1803.09574 See also <u>http://rpg.ifi.uzh.ch/docs/CVPR19workshop/CVPRW19\_Mike\_Davies.pdf</u>

Performance results are based on testing as of December 2018 and may not reflect all publicly available security updates. No product can be absolutely secure.

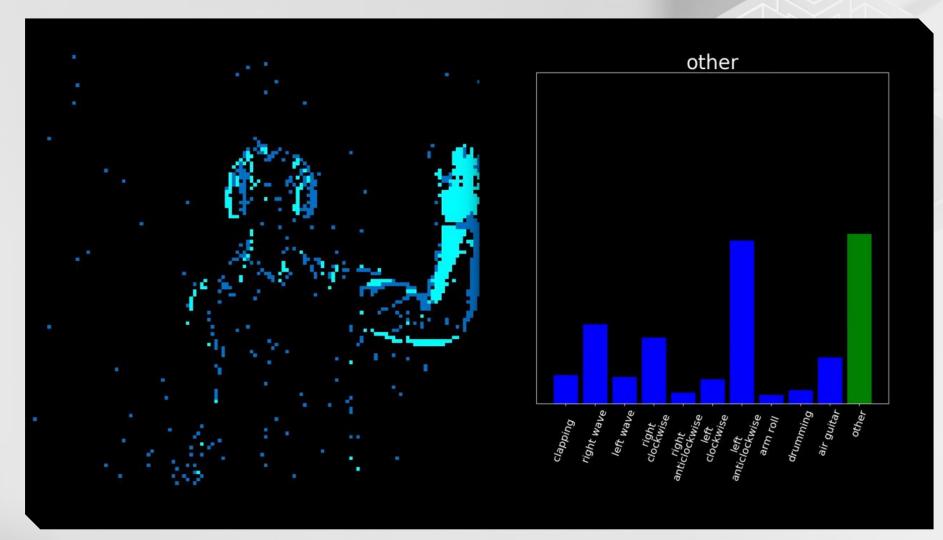

## **Event-Based Camera Gesture Recognition**

DAVIS240C\* 5mW static 5mW dynamic 1ms latency

<u>Loihi</u><sup>†</sup> 36mW static 7mW dynamic 10ms latency

\* iniVation DAVIS 240C performance numbers obtained from published specifications

<sup>†</sup> Intel Loihi measurements obtained using NxSDK v0.85 running on Wolf Mountain

Performance results are based on testing as of October 2019 and may not reflect all publicly available security updates. No product can be absolutely secure.

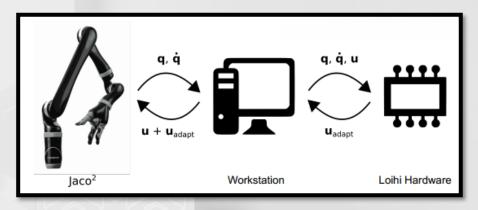

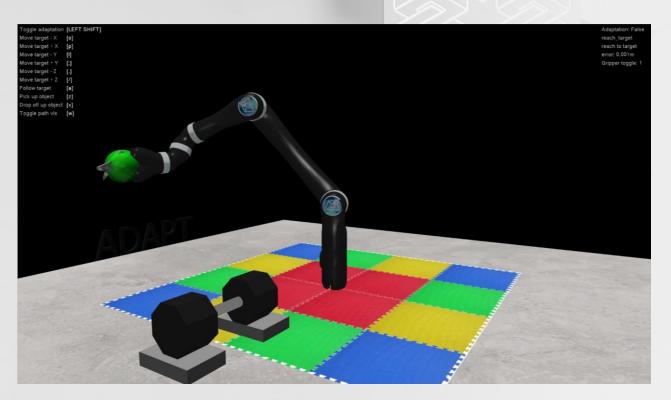

## Adaptive Control of a Robot Arm Using Loihi

- SNN adaptive dynamic controller implemented on Loihi allows a robot arm to adjust in real time to nonlinear, unpredictable changes in system mechanics<sup>[1][2]</sup>.

- Result outperforms standard PD & PID control algorithms.

[1] DeWolf, T., Stewart, T. C., Slotine, J. J., & Eliasmith, C. (2016, November). A spiking neural model of adaptive arm control. In *Proc. R. Soc. B* (Vol. 283, No. 1843, p. 20162134). The Royal Society.

[2] Eliasmith, "Building applications with next generation neuromorphic hardware." *NICE Workshop 2018*

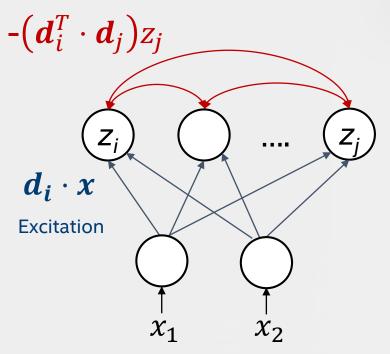

## LASSO Sparse Coding

#### The Spiking Locally Competitive Algorithm (S-LCA)

Neural Network Structure

Inhibition

Tang et al, arxiv: 1705:05475

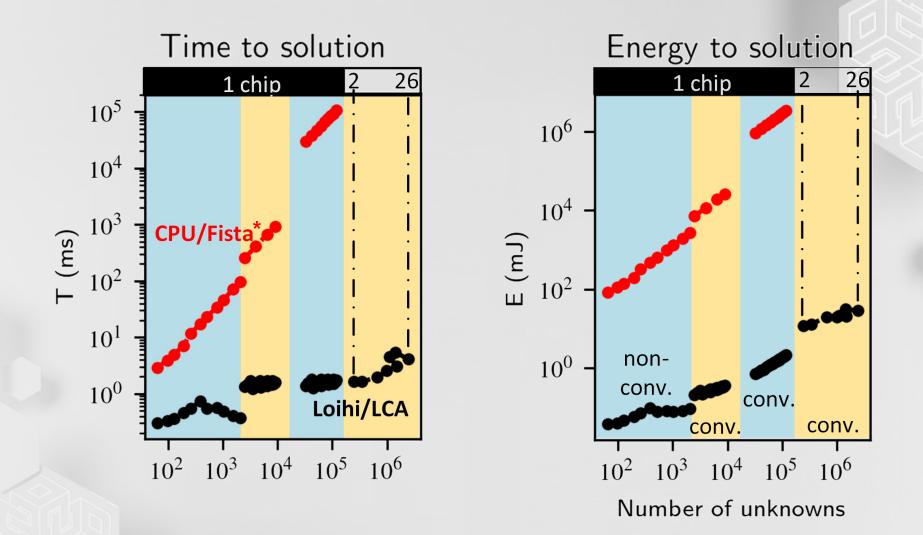

## LCA Solver for LASSO Scales Incredibly Well on Loihi

\* Intel Core i7-4790 3.6GHz w/ 32GB RAM. FISTA solver: SPAMS http://spams-devel.gforge.inria.fr/ Performance results are based on testing as of August 2019 and may not reflect all publicly available security updates. No product can be absolutely secure.

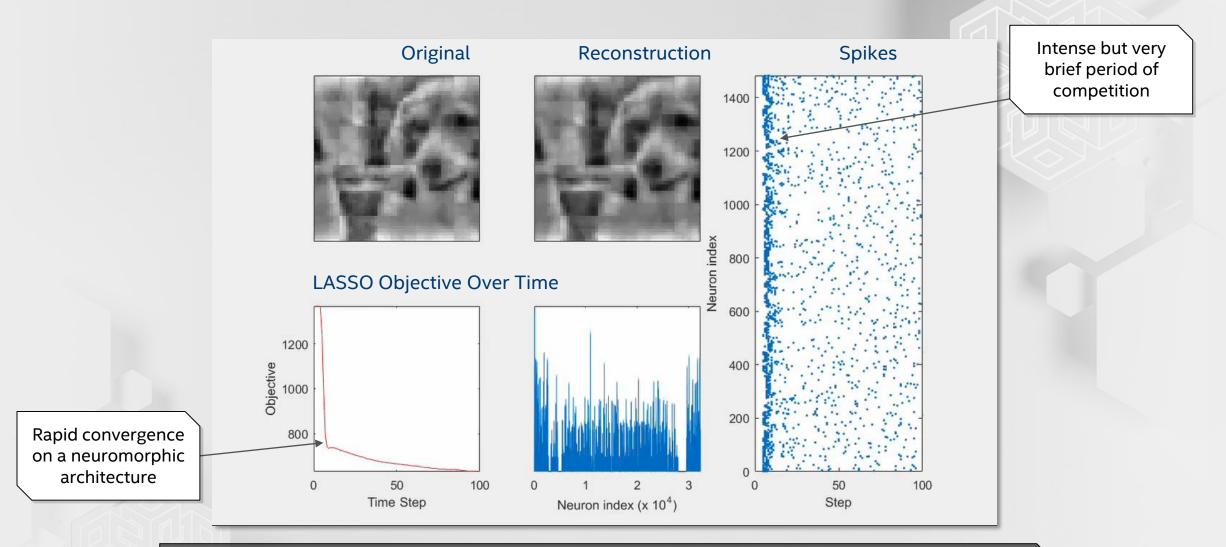

## Spiking LCA Dynamics on Loihi

Great efficiency comes from exploiting sparsity in space and time

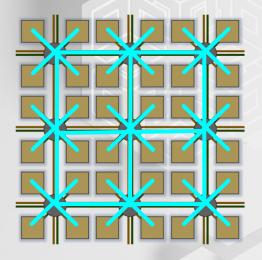

## Path Planning with Spikes

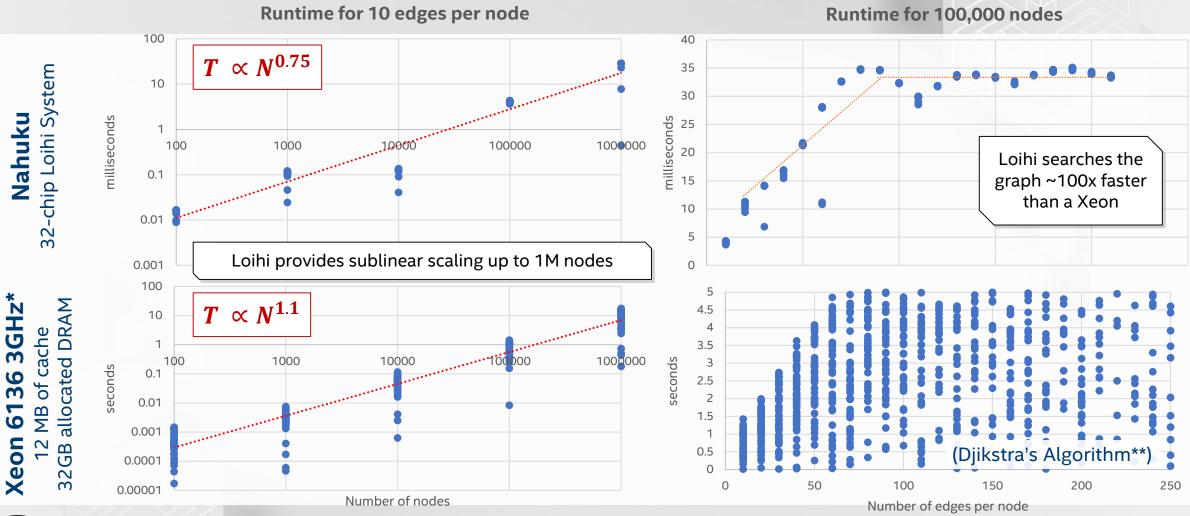

#### Runtime comparison to best Dijkstra optimizations:

- Neuromorphic:  $O(L \cdot \sqrt{V})$

- Standard: O(E)

#### For most nontrivial problems:

- L<<E</li>

- V<<E</li>

Neuromorphic solution uses fine-grain parallelism an temporal wavefrontdriven computation to potentially provide great performance gains for large problems.

Based on Ponulak F., Hopfield J.J. Rapid, parallel path planning by propagating wavefronts of spiking neural activity. Front. Comput. Neurosci. 2013. V. 7. Article № e98.

#### **ROBOT MOTION**

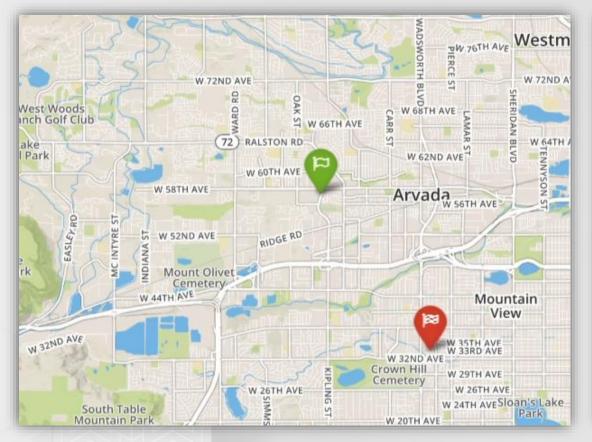

# Robot Location Service Location

#### DARPA SDR Site B (Data from Radish Robotics Dataset)

LOIHI REPRESENTATION

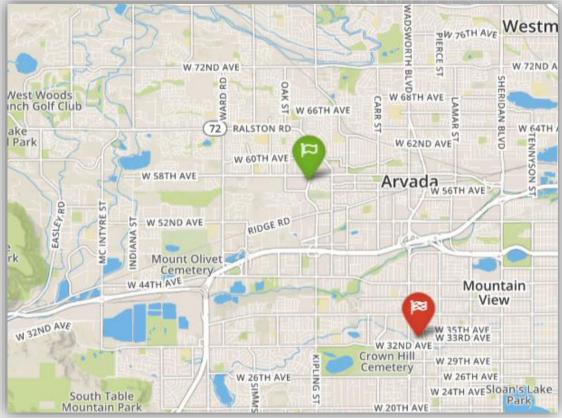

## Using Loihi for Driving Directions in Colorado

#### Loihi: Fine-Grain Parallel Search

#### Dijkstra: Sequential Breadth-First Search

More complex graphs give greater gains for Loihi

## Searching Small World Networks with Loihi

Watts-Strogatz network model with rewiring probability 20%.

#### \* Intel Xeon 6136 3.00 GHz w/ 32GB RAM.

#### \*\* with <u>NetworkX</u> graph analytics library

Performance results are based on testing as of December 2018 and may not reflect all publicly available security updates. No product can be absolutely secure.

## **The Research Frontier**

Loihi is the **first neuromorphic chip** to demonstrate **compelling scaling results** BUT THIS IS ONLY THE BEGINNING

## Come See Pohoiki Beach Live in the Intel Booth!

Email inrc\_interest @ intel.com for more information

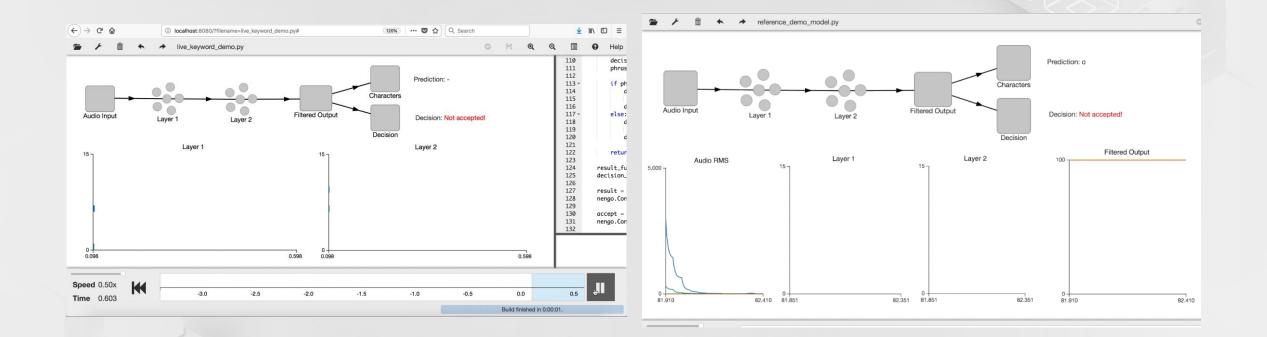

# **Keyword recognition**

(intel)